数理論理学では文字や記号で表現する

A = T -> B = T, A = F -> B = F

論理積OR

0,0 -> 0

0,1 -> 1

1,0 -> 1

1,1 -> 1

論理積AND

0,0 -> 0

0,1 -> 0

1,0 -> 0

1,1 -> 1

論理否定…インバータ

0 -> 1

1 -> 0

[ドモルガンの定理]

ある恒等式が成立していることがわかっていれば、その恒等式に含まれる0を1に、1を0に変換し、論理和を論理積に、論理積を論理和に変換して得られる式も恒等式として成り立つ

### 加法標準法

論理和を結合し、入力状態のうち、いずれか一つが起きた時に、F=1となるよう式を組む

### 乗法標準法

論理積で結合し、入力状態のうち、いずれか一つが起きた時に、F=0となるよう式を組む

### カルノー図

入力変数の値の組み合わせをもとに作成した行と列に出力の値を書き込んだ一覧

論理関数(4入力1出力、3入力2出力)などを簡素化できる

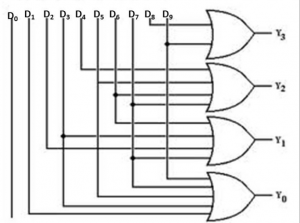

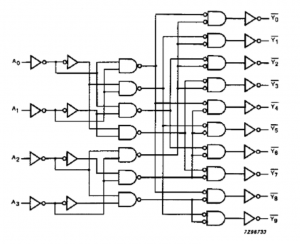

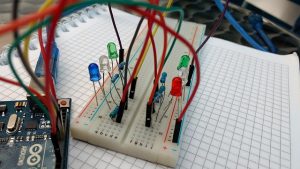

### 論理ゲート

基本回路を論理ゲート(logic gate)といい、通常一つの回路記号で表される

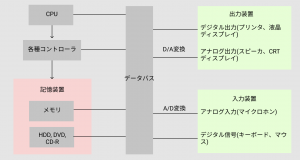

電圧が低い状態(Low)を0に、電圧が高い状態(High)を1に対応させる

どの半導体素子もデジタル回路ではオンとオフを伴ったスイッチの役割を担っている

### ダイオード

P形半導体(電子が不足)からの端子をアノード、N形半導体(余った電子がP原子の周りを回っている)からの端子をカソードといい、アノードからカソードの流れる電流のみを通して、その逆はほとんど通さない

P型は+の電圧、N型は-の電圧

整流作用があり、スイッチと同じ役割を持つ。順バイアスの電圧でオン、逆バイアスの電圧でオフとなり、半導体スイッチという

バイポーラトランジスタも IB>0 or IB = 0でスイッチの役割を果たす(Transistor Transistor Logicで広く使用)

論理回路出力に接続可能な最大ゲート数をファインアウトという

### MOSFET

ゲート、ドレイン、ソース

ゲート、ソース間が絶縁された小容量コンデンサ(直流通過、電荷を蓄える)と等価の構造担っている

一度充電されると、電流はほとんど流れずにオン状態を維持することができる為、電力消費が小さい

### CMOS

二つのMOSFETを直列に接続した構造(complementary MOS)

CMOSでは電源電圧Vccが出力端子から分離される為電流が流れず原理上電力損失は起こらない

CMOS回路では原理上電圧降下が生じない為、より多くのゲートを同時に接続できる

– ORゲート…論理和を実現する論理回路 いずれかがHの場合、ダイオードがオン

– ANDゲート…論理積を実現する回路 両者がHの場合はダイオードがオフ

– NOTゲート…バイポーラトランジスタで実現 AがLのとき、抵抗Rは電流が流れない為F=H 逆にA=Hにすると抵抗Rに電流が流れて電圧が低下する為F=Lとなる

NORゲート(ORとNOTゲートを組み合わせる) …AND, OR, NOTの基本ゲートを全て表現できる

NANDゲート(ANDとNOTゲートを組み合わせる) …AND, OR, NOTの基本ゲートを全て表現できる

なるほど、パソコンって、pn接合のダイオードで電圧処理してるのか

こりゃ、エンジニアは電子回路勉強した方が絶対いいな