Arduinoやラズパイを触ると、無精に触りたくなります。

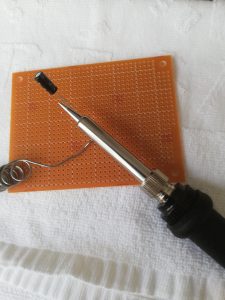

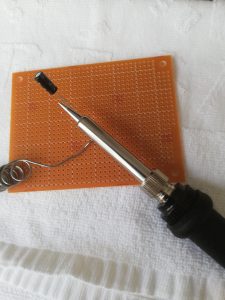

ということで、半田ごてセットを購入しました。

机に直置きは怖いので、タオルの上で作業します。

はんだ線を付けても全く溶解しなかったので不可解に思いましたが、ハンダゴテの金属が加熱するのに数分程度時間がかかるようで、少し時間をおいたらハンダ線が溶け始めました。

なんやこの臭いは? 臭いが強烈

作業は室内より室外の方が向いているように思いました。

しかし半田ごてはやりたかったことの一つ。

まあ、一歩前進はしました。

ソフトウェアエンジニアの技術ブログ:Software engineer tech blog

随机应变 ABCD: Always Be Coding and … : хороший

Arduinoやラズパイを触ると、無精に触りたくなります。

ということで、半田ごてセットを購入しました。

机に直置きは怖いので、タオルの上で作業します。

はんだ線を付けても全く溶解しなかったので不可解に思いましたが、ハンダゴテの金属が加熱するのに数分程度時間がかかるようで、少し時間をおいたらハンダ線が溶け始めました。

なんやこの臭いは? 臭いが強烈

作業は室内より室外の方が向いているように思いました。

しかし半田ごてはやりたかったことの一つ。

まあ、一歩前進はしました。

トランジスタとは電子回路において信号を増幅またはスイッチングすることができる半導体素子

– 信号を増幅する

– 回路をオンオフする

– NPNやPNPという順番で半導体を挟んでいる(Eエミッタ、Bベース、Cコネクタ)

– バイポーラ型トランジスタ、ユニポーラ型トランジスタ、フォトトランジスタ、サイリスタなどの種類がある

### トランジスタの使い方

微弱な電流を流してコレクタ電流を増幅させる

void setup() {

// put your setup code here, to run once:

Serial.begin(9600);

pinMode(8,OUTPUT);

}

void loop() {

// put your main code here, to run repeatedly:

Serial.println("HIGH");

digitalWrite(8,HIGH);

delay(2500);

Serial.println("LOW");

digitalWrite(8,LOW);

delay(2500);

}

コンデンサは電気を蓄えたり放電したりする

金属板が絶縁体を挟み込んだ状態となっている

電圧を加えられると放電する

電圧を一定する働きがある

1.電荷を貯める(静電容量)

2.直流電流は通さず、交流電流を通す(充電と放電を繰り返す)

3.周波数が高い交流ほど通しやすい(抵抗の働きをする)

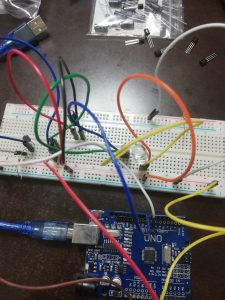

コンデンサ、トランジスタを組み込んで配線を組みます

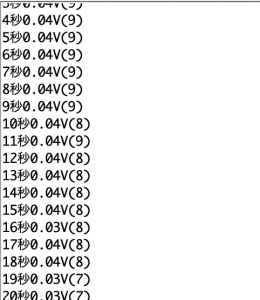

int count = 0;

boolean discharge = false;

void setup() {

// put your setup code here, to run once:

Serial.begin(9600);

pinMode(8, OUTPUT);

pinMode(9, OUTPUT);

digitalWrite(8, HIGH);

digitalWrite(9, LOW);

Serial.println("コンデンサの充電開始");

delay(1000);

}

void loop() {

// put your main code here, to run repeatedly:

count++;

Serial.print(count);

Serial.print("秒");

Serial.print(analogRead(A0) / 1024.0 * 5.0);

Serial.print("V");

Serial.print("(");

Serial.print(analogRead(A0));

Serial.println(")");

if(count >= 35 && !discharge){

digitalWrite(8, LOW);

digitalWrite(9, HIGH);

Serial.println("コンデンサの放電開始");

count = 0; discharge = true;

}

delay(1000);

}

– DDR4メモリはランダムアクセスメモリの最新世代

L メモリは各世代ごとに速度と周波数が向上している

L メモリの各世代によって電気パラメーターが異なる

– DDR2(1.8V)はXP,Vista, DDR3(1.5V)はWindows 7、DDR4(1.2V)はWindows 10

– ダブルデータレートメモリは、クロック信号の上昇端と下降端の両方でプロセッサーにデータを転送する

– クロック信号は、ダウンビートとアップビートの両方で構成される

– ダブルデータレートメモリの速度はデータ転送に単一端のみを使用するシングルデータレートメモリに比べ大幅に高速

– メモリーに取り付けられている金属製のものをヒートスプレッダという

### DRAMメーカー

Samsung(約45%シェア), SK Hynix(韓国 約28%), Micron(約23% Crucialシリーズ), Nanya(台湾), Winbond(台湾), Powerchip(台湾)

### 設計

– DDR4-2400、DDR4-2666などを チップ規格、PC4-19200やPC4-21300などを モジュール規格

– メモリ基盤にメモリチップを半田付けする

L メモリチップは集積回路であり、各チップ上にはさまざまなトランジスタ、抵抗、およびコンデンサが形成されている

メモリチップもCPUのように論理回路を設計してシリコンから作られているのか。。

つまり、メモリ、CPU、マザーボードにしろ、何やるにしろ集積回路、回路設計の知識が必須と言う事か。。

Godem

電気回路: 正弦波(サイン波)交流に対する回路素子の振る舞い、インピーダンスという概念理解

制御工学: 任意の入力(例えばステップ波形など)に対する回路の応答を解析

アナログ電子回路: トランジスタの構造や特徴を理解、信号増幅の原理の理解や小信号解析といった手法

やればやるほど勉強しなきゃいけない事多すぎんな

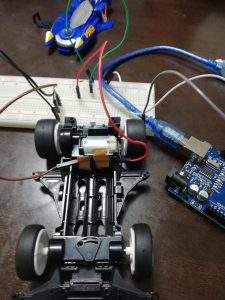

とりあえずモータが届いたので、ミニ四駆のモータ電源をarduinoから供給できるようジャンプワイヤーを無理やりミニ四駆に接着します。

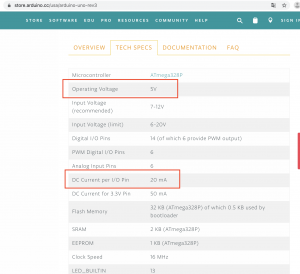

単三電池だと上手く動くが、arduinoだと動かないのは何故だろう??

Arduinoのデジタルピンの電流は40mAなので、どうやらモーターで必要な200mAに足りていないらしい。

※tech specのDC current per I/O Pinってところが出力電流らしい。

電流を増幅するにはトランジスタを使うみたいね。

ん? また部品買うのか? 全然進まねー、もうやだああああああああああああああああああああ

### 考察

ミニ四駆をマイコンで制御する場合、モーターのオンオフや回転数ぐらいしか制御できない

右折、左折をコントロールするには前輪タイヤにステアリング機能を付けないといけない

※ミニ四駆では前輪、後輪共に直線

ステアリングは、arduinoの電圧を変えると、向きが左右に動くようにしなければならない

モータを制御できるということは、他の駆動系(電車、飛行機、ドローンなど)も理論上はarduinoで動かせるが、ステアリング同様に、その仕組みを作るらなければならず、機能を理解して資材をゼロから用意してハードルが高い

一通り部品を用意していざ動かしてみても、問題が発生し、それが部品に起因している場合は、また資材を買わなければならず、時間がかかる

ステアリング付きのミニ四駆にカメラを装着すれば、理論上は自動運転も不可能ではない筈

### 対策

自分で想像して作るよりも、完成物を分解して作った方が時間の節約になる

しかし、ミニ四駆って、自分が子供だった頃と殆ど変わってないけど、この仕組みをこの低単価で提供しているTAMIYAは偉大な会社なんだと理解しました。

FPGAとは?

-> Field Programmable Gate Arrayの略

-> 現場で書き換え可能な論理回路の多数配列:ハードウェア言語で修正が出来るデバイス

ハードウェア言語とは一般的に半導体の回路記述をする際に用いる言語

論理回路とはデジタル信号を扱う回路のこと

論理合成と配置配線はハードウェア言語で記述された回路をFPGAに書き込む為のデータに変換すること

CPLDは汎用ロジックIC数百個~数千個分の回路を内部で構成できる

LSIを超える規模の回路を簡単に構成できる

PLGの一種

【組み込み系の開発工程】

要求分析→要件定義→基本設計・詳細設計→RTL設計(Verilog、VHDLなどを用いてコーディング) →論理合成→動作シミュレーション→配置配線

ビッグデータのデータ処理やディープラーニング向けの並列計算等にFPGAやASICが使われることもある

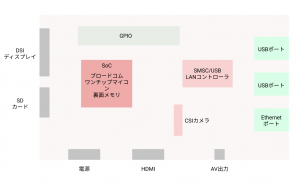

SoC(System-on-a-Chip)と呼ばれるLSIはCPU、GPU、メモリを含む

Raspberry Pi 3 model BのCPUはARM社

– Broadcom BCM2837

– 1.2GHz 64-bit quad-core ARMv8 Cortex-A53

– メモリ1GB LPDDR2 SDRAM

DSI(Display Serial Interface)を備えたディスプレイは、タッチ操作が可能

取り敢えず、macからmicrobで電源供給して、OSインストールまでは出来た^^

ヒャッホー

USBキーボードがないとInputが出来ないので、キーボード待ちだけど、IoTコミュニティーに入る第一歩は踏み出せたかな。

がはははは

### マスクROM

メモリセルの内部回路の開放と短絡によって1, 0を記憶する

半導体製造工程には写真の感光技術が利用されるが、基板を覆うマスクパターンによってデータが記録される

データ線ADとデータ線Dが短絡しており、AD=HとなるとD=Hとなる

アドレス線を開放状態にすると、AD=HとしてもD=Lのままである H, Lに0と1を割り当てて、1ビットを記憶することができる

バイポーラトランジスタを使ったマスクROMはこの原理で動作させてることができる

実用的には消費電力の少ないMOSFETを半導体スイッチとして用いている

マスクROMはIC製造段階で情報を書き込むのでデータを変更することができない

### PROM

一度だけ書き込み可能なROMをPROMという

ヒーズをトランジスタのエミッタ端子とデータ線の間に設けて、これを溶断するかどうかによってH、Lを記憶する

PROM出荷時には全ヒューズが繋がっている

セルにLを記憶するには、電源電圧Vccを高く設定し、ヒューズが溶断されるとLが記憶される

ヒューズ以外にもダイオードを挿入し、pn接合を破壊・短絡してH, Lを表す方法もある

### EPROM

データの正気と再書き込み可能なROMをEPROMという

データの消去に紫外線を使うUV-EPROMと電圧を使うEEPROMがある

装置固有の設定データや利用者情報などの記憶、書き換え頻度の少ない用途に適している

– 書き込み方法

p型半導体基板上にn型半導体を二つ設け、これに電極ドレイン(D)とソース(S)をつける

更にドレイン・ソース間に絶縁層を設け、その上にゲート電極(G)をつける

n型半導体は自由電子が含まれた物質で自由電子の流れが電流

p型半導体は自由電子を含んでいない

ゲートに電圧を加えない状態では電流は流れない(nMOSがオフ)

ゲートに電圧を加えるとゲート、ソース間はコンデンサとして働き、正の電荷がゲート電極に蓄えられる

-> nチャンネルを作り、半導体スイッチとなる Vgs > Vthでオン、Vgs < Vthでオフ

FGの帯電量によってMOSFETのオンオフを決定でき、ROMとして1ビットを記憶させることができる

一度入り込んだ負電荷は電源を切っても消えないので、半永久的にこの状態を保持できる

- データ消去

UV-FPROMは紫外線をFGゲートに照射させることで内部電子のエネルギーを増大させ、FGゲートから放出させる

このため、IC上部には紫外線照射窓がある

EEPROMは電圧によってFGゲートの電子を放出させる FGゲートの帯電動作と逆

ゲート電圧を0とし、ドレイン電圧を高く設定するとFGゲートの電子がドレイン側に逃げ出して0となる EEPROMは電圧制御によって1ビット単位で行うことができるが、セルにMOSFETが追加されるため面積が大きくなり大容量化が難しくなる

### フラッシュメモリ

メモリセルを幾つかの集合に分割し、消去をブロック単位で行うようにした

セルの消去用トランジスタをなくすことでセル面積を抑え、大容量化を図っている

電源を切ってもデータが保持できるので応用は急速に広がっている

マザーボードのBIOS、スマホのストレージはフラッシュメモリー

UBS, SSDなどもNAND型のフラッシュメモリー

フラッシュメモリはTranscend(台湾)、Silicon-Power(ドイツ)、ELECOM、I-O DATA、SanDisk、BUFFALO、GREEN HOUSEなどが生産

EPROMの仕組みは、p型半導体と、s,dのn型半導体に挟まれた絶縁体のゲートでできてるのね。

1ビットでこの仕組みが必要なのに、500GBのSSDって、どれだけpnとデータ線、アドレス線をどうやって少量化して詰め込んでるんやろうか、全く想像が付かない。CPUもそうだけど。

ICメモリの仕組みがわかったところで、アプリケーションの品質には直接は影響はないけど、興味深いところではある。

記憶装置には大きく分けて外部記憶装置と内部記憶装置がある

### 外部記憶装置

外部記憶装置にはハードディスク、CD、DVDなど

-> 機械的な駆動部分が存在するため読み書き速度が遅い

### 内部記憶装置

ICメモリは小型の回路部品であり、基板内部に組み込まれる為、内部記憶装置と言われる

記憶容量では劣るが、機械駆動部が少ない為高速

CPU周りの高速処理にICメモリが使われている

### ICメモリの内部構造

大量の2値情報を記憶する

IC内部の最小記憶単位をセルと良い、通常は1ビットを記憶する

セルは平面上に配列されており、アクセスするためにアドレス(固有の識別番号)が使われている

行アドレスと列アドレスがあり、アドレス線の電圧がH(アクティブ)になり、列アドレスが入力されると、特定のデータ線が選ばれ、セルが読み書きの対象となる

読み書きの制御信号R/WがHになると、記憶データが出力され、Lになると記憶される

### ICメモリの分類

ROM: 読み込み専用、電源を切っても内容保持 R/W制御信号は取り除かれ、出力のみ

RAM: 読み込み書き込み自由、電源を切ると内容も消える R/W信号に応じて双方向通信に対応

メモリっていうと、文字データ、画像データなどを記憶しているように思っていたが、実際には0、1の2値データを持ってるだけなのね。えらい勘違いをしていたみたいだ。