#include <GL/glut.h>

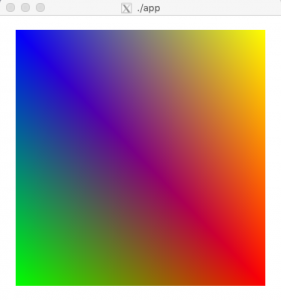

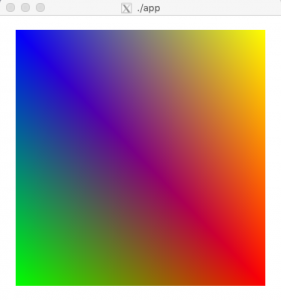

void display(void){

glClear(GL_COLOR_BUFFER_BIT);

glRotated(25.0, 0.0, 1.0, 0.0);

glBegin(GL_POLYGON);

glColor3d(1.0, 0.0, 0.0);

glVertex2d(-0.9, -0.9);

glColor3d(0.0, 1.0, 0.0);

glVertex2d(0.9, -0.9);

glColor3d(0.0, 0.0, 1.0);

glVertex2d(0.9, 0.9);

glColor3d(1.0, 1.0, 0.0);

glVertex2d(-0.9, 0.9);

glEnd();

glFlush();

}

void init(void){

glClearColor(1.0, 1.0, 1.0, 1.0);

}

int main(int argc, char *argv[]){

glutInit(&argc, argv);

glutInitDisplayMode(GLUT_RGBA);

glutCreateWindow(argv[0]);

glutDisplayFunc(display);

init();

glutMainLoop();

return 0;

}

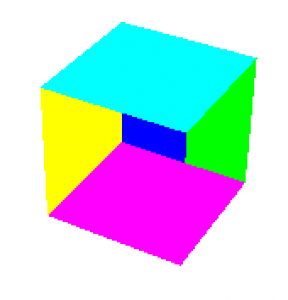

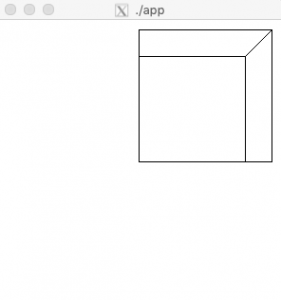

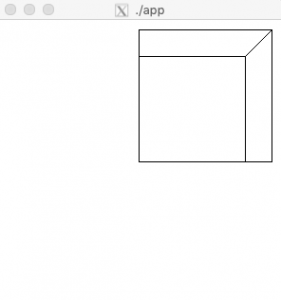

glRotated() による回転の行列が積算されている

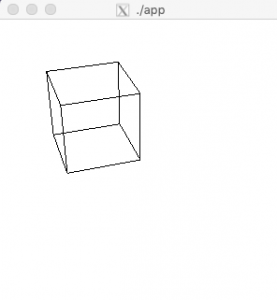

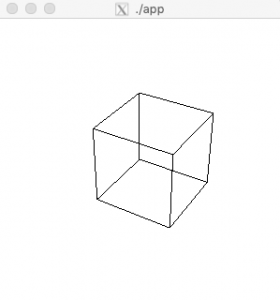

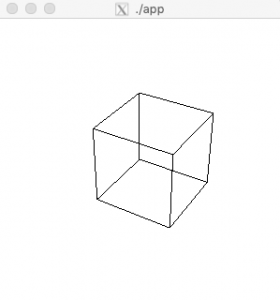

### 線画を表示する

#include

GLdouble vertex[][3] = {

{0.0, 0.0, 0.0},

{1.0, 0.0, 0.0},

{1.0, 1.0, 0.0},

{0.0, 1.0, 0.0},

{0.0, 0.0, 1.0},

{1.0, 0.0, 1.0},

{1.0, 1.0, 1.0},

{0.0, 1.0, 1.0}

};

int edge[][2] = {

{0, 1},

{1, 2},

{2, 3},

{3, 0},

{4, 5},

{5, 6},

{6, 7},

{7, 4},

{0, 4},

{1, 5},

{2, 6},

{3, 7}

};

void display(void){

int i;

glClear(GL_COLOR_BUFFER_BIT);

/* 図形の描画 */

glColor3d(0.0, 0.0, 0.0);

glBegin(GL_LINES);

for(i = 0; i < 12; ++i){

glVertex3dv(vertex[edge[i][0]]);

glVertex3dv(vertex[edge[i][1]]);

}

glEnd();

glFlush();

}

void resize(int w, int h){

glViewport(0, 0, w, h);

glLoadIdentity();

gluPerspective(30.0, (double)w / (double)h, 1.0, 100.0);

glTranslated(0.0, 0.0, -5.0);

}

void init(void){

glClearColor(1.0, 1.0, 1.0, 1.0);

}

int main(int argc, char *argv[]){

glutInit(&argc, argv);

glutInitDisplayMode(GLUT_RGBA);

glutCreateWindow(argv[0]);

glutDisplayFunc(display);

glutReshapeFunc(resize);

init();

glutMainLoop();

return 0;

}

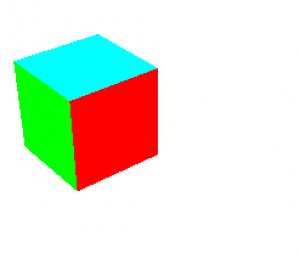

### 視点の位置を変更する

(3,4,5) の位置から原点 (0,0,0) を眺める

void resize(int w, int h){

glViewport(0, 0, w, h);

glLoadIdentity();

gluPerspective(30.0, (double)w / (double)h, 1.0, 100.0);

gluLookAt(3.0, 4.0, 5.0, 0.0, 0.0, 0.0, 0.0, 1.0, 0.0);

}

凄い。