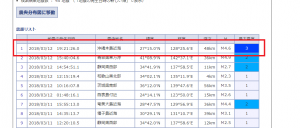

まず気象庁

———–

地震の発生日時 震央地名 緯度 経度 深さ M 最大震度

1 2018/03/12 19:21:26.0 沖縄本島近海 27°15.0′N 128°25.6′E 48km M4.6 3

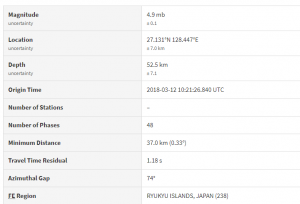

USGS

———-

Magnitude

uncertainty

4.9 mb

± 0.1

Location

uncertainty

27.131°N 128.447°E

± 7.0 km

Depth

uncertainty

52.5 km

± 7.1

Origin Time 2018-03-12 10:21:26.840 UTC

Number of Stations –

Number of Phases 48

Minimum Distance 37.0 km (0.33°)

Travel Time Residual 1.18 s

Azimuthal Gap 74°

FE Region RYUKYU ISLANDS, JAPAN (238)

時間はほぼ一緒ですが、マグニチュード、緯度経度、depth、全て値が微妙に異なります。

マグニチュード:地震が発するエネルギーの大きさを対数で表した指標値

地震のエネルギーを1000の平方根を底とした対数で表した数値で、マグニチュードが 1 増えると地震のエネルギーは約31.6倍になり、マグニチュードが 2 増えると地震のエネルギーは1000倍になる

マグニチュード測定方法:地震計

USGS:GPSや地震計を一定間隔で配備して、ネットワーク化、地下深くまでドリルで穴を開けて分析

気象庁とUSGSでは、どちらのデータが精度が高いのか疑問に思ったのですが、

下記資料をざっと流し読みすると、やってる事にあまり違いがないように感じます。

http://www.spaceref.co.jp/homepage/colum/images/US_earthquake_observation.pdf

ということで、今回は、USGSのデータを使って、地震情報をつくっていきたいと思います。