色々できそうですね♪

<!DOCTYPE html>

<html lang='ja'>

<head>

<title>api</title>

<meta charset='utf-8'>

</head>

<body>

<?php

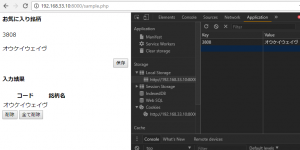

$rakuten_result = getRakutenResult('adidas', 1000);

foreach ($rakuten_result as $item):

?>

<div style='margin-bottom:20px; padding:30px; border:1px solid #000; overflow:hidden;'>

<div style='float: left;'><img src='<?php echo $item['img']; ?>'></div>

<div style='float: left; padding: 20px;'>

<div><?php echo $item['name']; ?></div>

<div><a href='<?php echo $item['url']; ?>' target_"blank"><?php echo $item['url']; ?></a></div>

<div><?php echo $item['price']; ?>円</div>

<div><?php echo $item['shop']; ?></div>

</div>

</div>

<?php

endforeach;

?>

</body>

</html>

<?php

function getRakutenResult($keyword, $min_price){

$baseurl = 'https://app.rakuten.co.jp/services/api/IchibaItem/Search/20170706';

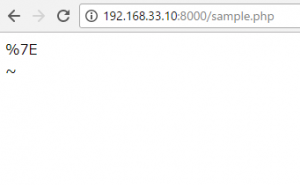

function urlencode_rfc3986($str){

return str_replace('%7E','~', rawurlencode($str));

}

$params = array();

$params['applicationId'] = '***';

$params['keyword'] = urlencode_rfc3986($keyword);

$params['sort'] = urlencode_rfc3986('+itemPrice');

$params['minPrice'] = $min_price;

$params['genreId'] = '509057';

$canonical_string='';

foreach($params as $k => $v){

$canonical_string .= '&' .$k. '=' .$v;

}

$canonical_string = substr($canonical_string, 1);

$url = $baseurl . '?' . $canonical_string;

$rakuten_json=json_decode(@file_get_contents($url, true));

print_r('<pre>');

var_dump($rakuten_json);

print_r('</pre>');

$items = array();

foreach($rakuten_json->Items as $item) {

$items[] = array(

'name' => (string)$item->Item->itemName,

'url' => (string)$item->Item->itemUrl,

'img' => isset($item->Item->mediumImageUrls[0]->imageUrl) ? (string)$item->Item->mediumImageUrls[0]->imageUrl : '',

'price' => (string)$item->Item->itemPrice,

'shop' => (string)$item->Item->shopName,

);

}

return $items;

}

?>