コンピュータの構成要素は、入力部、記憶部、演算部、出力部、制御部からなる。

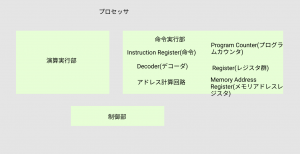

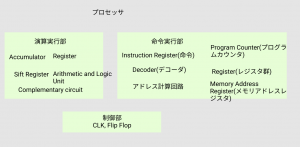

一般的に演算部と制御部をまとめたものをプロセッサとして実現する

機械語がプロセッサを実行する

### 汎用プロセッサ

CPU

1チップで実現されたプロセッサをマイクロプロセッサという

例えば、通信制御プロセッサやデータベースプロセッサなど

### 専用コンピュータ

用途に合わせてプロセッサ自体も設計する

画像処理用プロセッサ…GPU

デジタル信号処理用プロセッサ…DSP

LSI設計用プロセッサ…CAD

命令実行部の構成回路

Program Counter

– 実行するプログラムの主記憶装置の先頭アドレス

– 命令はInstruction Registerで保持される

レジスタ群

– MARにデータアドレスが入れられ、それによって主記憶装置上のデータから読み出す

– データはレジスタに入れられる

Decoder

– 命令を解読する

– 選択された信号を制御部に渡す

アドレス計算回路

– 演算実行対象となるデータの読み出しのアドレスを計算して求める場合がある

演算実行部はデータに対する演算加工を実行する

クロック回路はクロック信号が発生するごとに動作を一つ一つ進めていく

-構成回路間の接続

各回路間はデータや制御信号の受け渡しのために接続される

直接接続と、バス線を設け、これに各回路を接続するバス回路方式がある

### アーキテクチャー

CPUアーキテクチャ

– 命令セット

命令語の構成、形式、種別、数の表現方法、オペランドの指定方法などを定める

– システム制御

割り込み方式、システムを管理するためのアクセス権利設定などを定める

– プロセッサ内部構造

回路構成および高速化のための制御方式の設計

メモリアーキテクチャ

主記憶がもつ物理的容量を超えた領域を含めたアドレスをどのように指定制御するか

入出力アーキテクチャ

入出力動作に関する命令又は司令をどのような方式で行うか

### 命令

命令の形式には命令部と一つ以上のオペランド部から構成される

– 命令部 + R1 + R2 : Add , 1, 2

– 命令部 + R + メモリアドレス : Add, 1, 2のメモリアドレス

– 命令部 + データ + メモリアドレス

– 命令部 + メモリアドレス1 + メモリアドレス2 : Add, 1のメモリアドレス, 2のメモリアドレス

– 命令部のみ

直接アドレス指定、間接アドレス指定(ポインタ)があある

命令、アドレスモード(AM)、オペランド1、オペランド2

### 動作の流れ

プロセッサの処理は予め用意されたプログラムによって処理される

プログラムカウンタ(PC)からプログラムを命令を読み出し、命令レジスタ(IR)に入れられる

命令デコーダ(DEC)で解読を行い、アドレス計算回路でレジスタもしくはデータに命令を出す

レジスタから演算回路を使用し、演算回路で演算を実行する

演算結果はレジスタもしくはメモリに返される

linuxの物理プロセッサーの表示

vagrant@ubuntu-bionic:~/dev$ grep physical.id /proc/cpuinfo | sort -u | wc -l

1

-命令の概要

データ転送、演算、ストリング操作、ビット操作、プログラム転送、プロセッサコントロール

なるほど、メモリ上のプログラムから、プロセッサを通じて演算処理が行われていることは理解しました。